# **MOTOROLA**

# Switch Mode Power Supply with **Multiple Linear Regulators and High Speed CAN Transceiver**

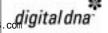

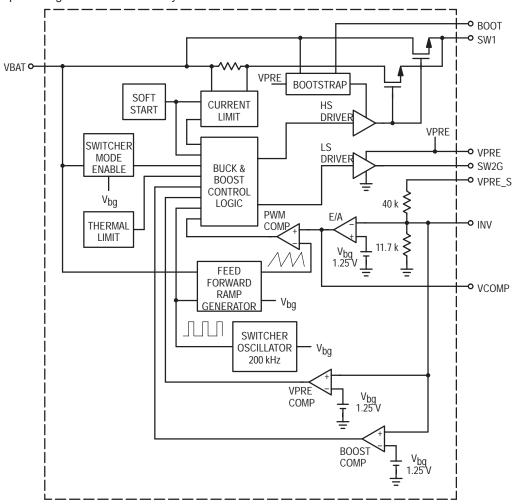

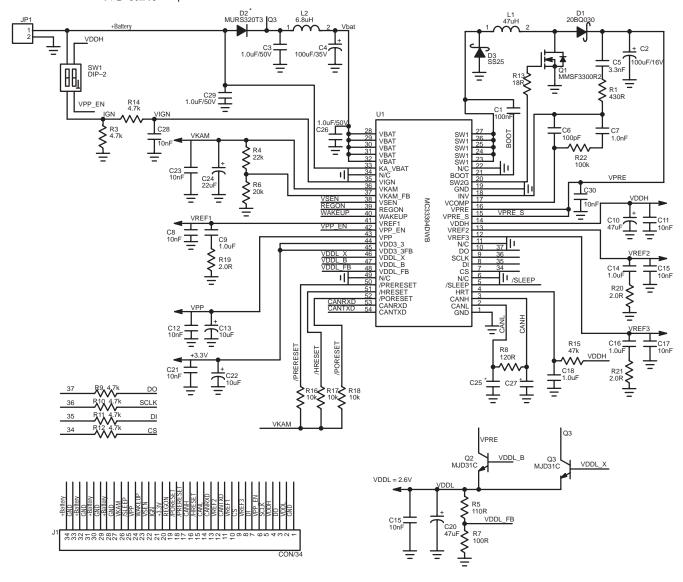

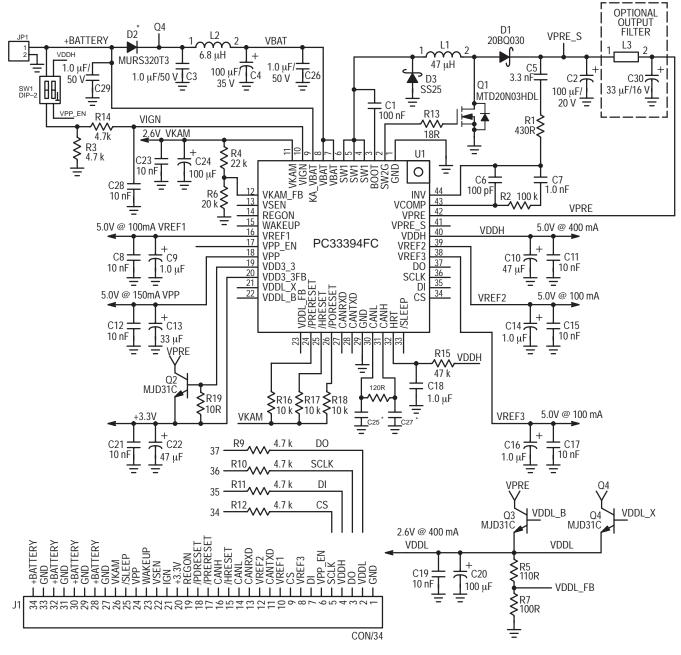

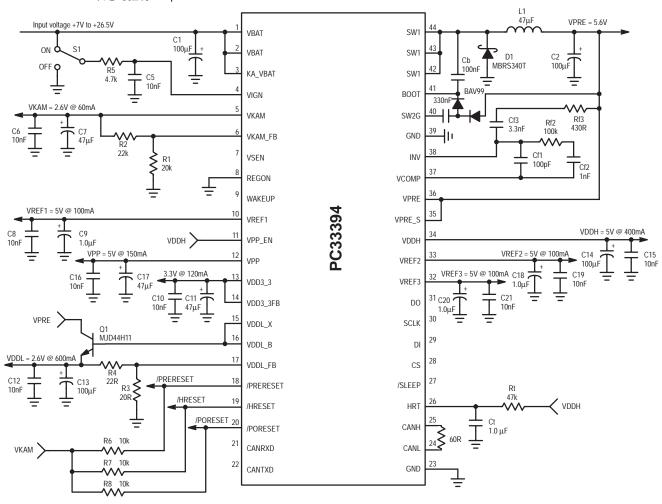

The 33394 is a multi-output power supply integrated circuit with high speed CAN transceiver. The IC incorporates a switching pre-regulator operating over a wide input voltage range from +4.0V to +26.5V (with transients up to 45V).

The switching regulator has an internal 3.0A current limit and runs in both buck mode or boost mode to always supply a pre-regulated output followed by Low Drop Out (LDO) regulators: VDDH / 5.0V @ 400mA; VDD3\_3 / 3.3V @ 120mA; VDDL / 2.6V (User scalable between 3.3V - 1.25V) @ 400mA typically, using an external NPN pass transistor. The Keep Alive regulator VKAM (scalable) @ 50mA; FLASH memory programming voltage VPP / 5.0V or 3.3V @ 150mA; three sensor supply outputs VREF(1,2,3) / 5.0V (tracking VDDH) @ 100mA each; and a switched battery output (VSEN) to supply 125mA clamped to 17V.

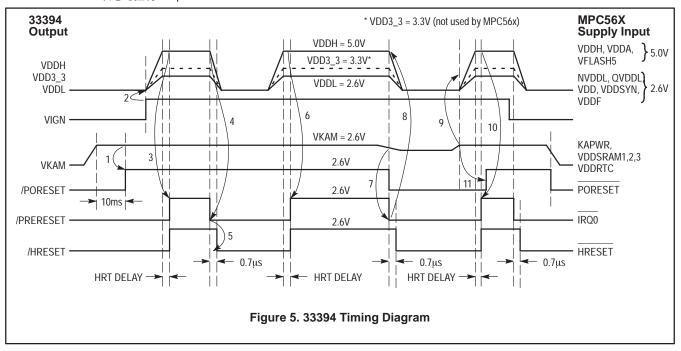

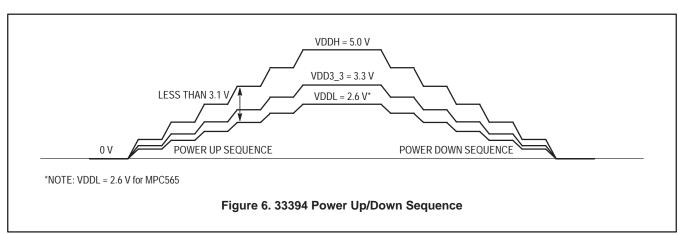

Additional features include Active Reset circuitry watching VDDH, VDD3\_3, VDDL and VKAM, user selectable Hardware Reset Timer (HRT), Power Sequencing circuitry guarantees the core supply voltages never exceed their limits or polarities during system power up and power down.

A high speed CAN transceiver physical layer interfaces between the microcontroller CMOS outputs and differential bus lines. The CAN driver is short circuit protected and tolerant of loss of battery or ground conditions.

33394 is designed specifically to meet the needs of modules, which use the MPC565 microcontroller, though it will also support others from the MPC5XX family of Motorola microcontrollers.

#### Features:

- Wide operating input voltage range: +4.0V to +26.5V (+45V transient).

- Provides all regulated voltages for MPC5XX MCUs and other ECU's logic and analog functions.

- Accurate power up/down sequencing.

- Provides necessary MCU support monitoring and fail-safe support.

- Provides three 5.0 V buffer supplies for internal & external (short-circuit protected) sensors.

- Includes step-down/step-up switching regulator to provide supply voltages during different battery conditions.

- Interfaces Directly to Standard 5.0V I/O for CMOS Microprocessors by means of Serial Peripheral Interface.

This document contains information on a new product. Specifications and information herein are subject to change without notice.

# 33394

## MULTI-OUTPUT POWER SUPPLY

**SEMICONDUCTOR TECHNICAL DATA**

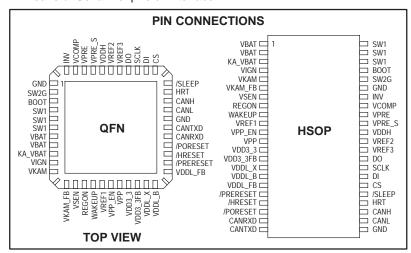

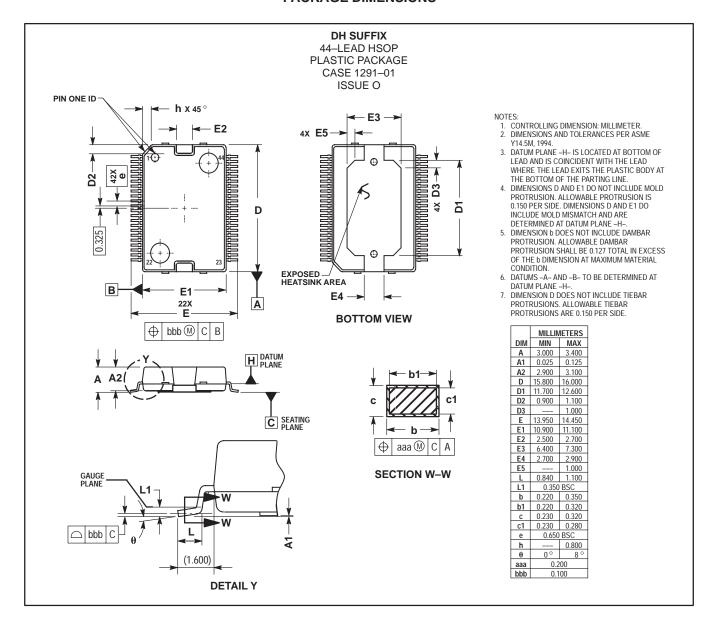

44-Lead HSOP **DH SUFFIX CASE 1291**

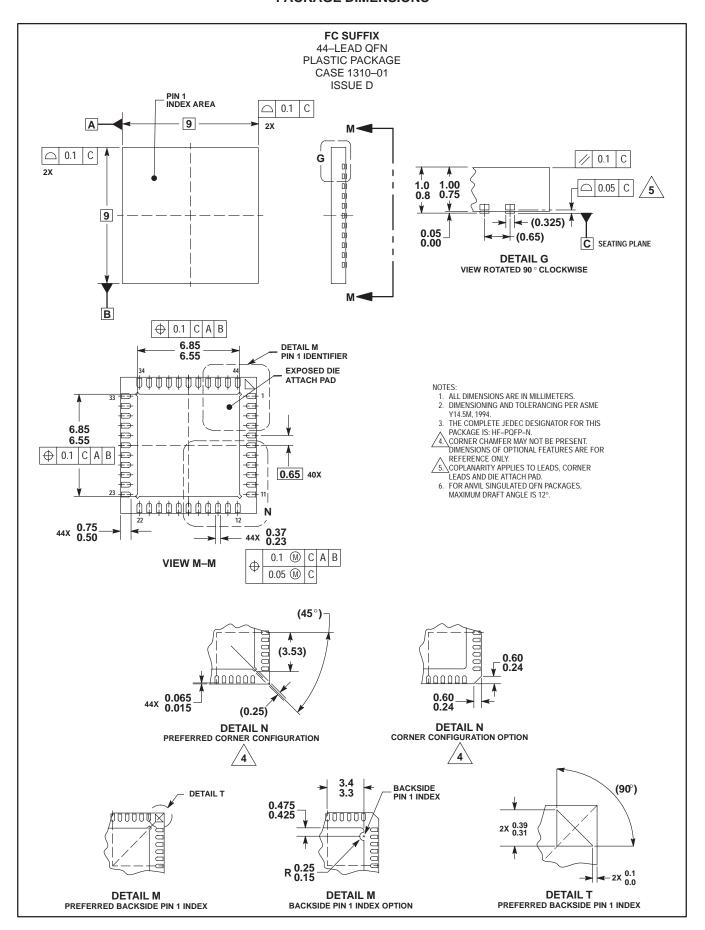

44-Lead QFN **FC SUFFIX CASE 1310** (BOTTOM VIEW)

54-Lead SOICW-EP **DWB SUFFIX CASE 1377**

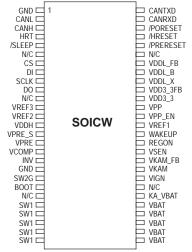

# PIN CONNECTIONS

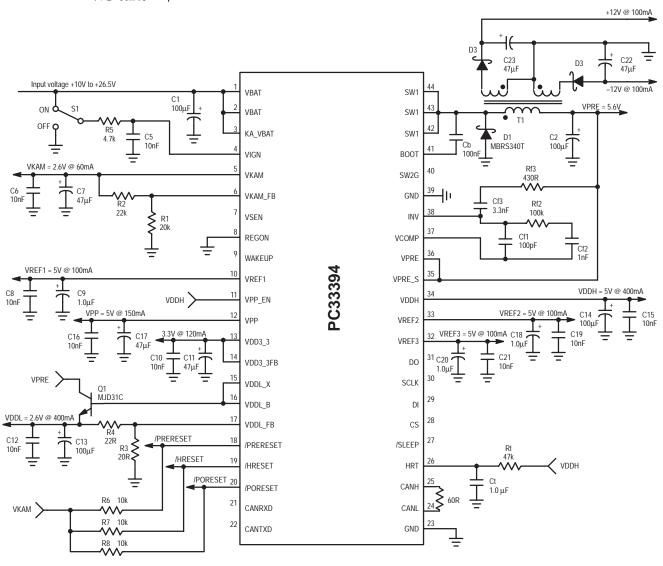

Notes: 1. In this configuration the device can operate with a minimum input voltage VBAT of 4.0 V (voltage at 33394 VBAT pins).

- 2.VDDL and VKAM are adjustable to support current microprocessor technology (1.25 V to 3.3 V) by means of an external resistor divider.

- 3. When the 33394 CAN transceiver is not used, CANL and CANH pins can be shorted together.

- 4. Dp1 = reverse battery protection diode. Dp2 = load dump protection diode. Dp1, Dp2 can be ommitted in those applications which do not require such protection.

# PIN FUNCTION DESCRIPTION (44-HSOP Package)

| PIN NO. | NAME      | DESCRIPTION                                                                            |

|---------|-----------|----------------------------------------------------------------------------------------|

| 1       | VBAT      | Battery supply to IC (external reverse battery protection needed in some applications) |

| 2       | VBAT      | Battery supply to IC (external reverse battery protection needed in some applications) |

| 3       | KA_VBAT   | Keep alive supply (with internal protection diode)                                     |

| 4       | VIGN      | Turn-On control through ignition switch (with internal protection diode)               |

| 5       | VKAM      | VDDL tracking Keep Alive Memory (Standby) supply                                       |

| 6       | VKAM_FB   | VKAM output feedback                                                                   |

| 7       | VSEN      | Switched battery output                                                                |

| 8       | REGON     | Regulator "Hold On" input                                                              |

| 9       | WAKEUP    | CAN wake up event output                                                               |

| 10      | VREF1     | VDDH tracking linear regulator 1                                                       |

| 11      | VPP_EN    | VPP enable                                                                             |

| 12      | VPP       | 5.0 V/ 3.3 V FLASH memory programming supply, tracking VDDH/VDD3_3                     |

| 13      | VDD3_3    | 3.3 V regulated supply output, base drive for optional external pass transistor        |

| 14      | VDD3_3FB  | VDD3_3 output feedback                                                                 |

| 15      | VDDL_X    | VDDL optional external pass transistor base drive, operating in Boost Mode only        |

| 16      | VDDL_B    | VDDL external pass transistor base drive                                               |

| 17      | VDDL_FB   | VDDL output feedback                                                                   |

| 18      | /PRERESET | Open drain /PRERESET output, occurs 0.7 us prior to /HRESET (Hardware Reset)           |

| 19      | /HRESET   | Open drain / HRESET (Hardware Reset) output                                            |

| 20      | /PORESET  | Open drain / PORESET (Power On Reset) supervising VKAM supply to the microprocessor.   |

| 21      | CANRXD    | CAN receive data (DOUT)                                                                |

| 22      | CANTXD    | CAN transmit data (DIN)                                                                |

| 23      | GND       | Ground                                                                                 |

| 24      | CANL      | CAN differential bus drive low line                                                    |

| 25      | CANH      | CAN differential bus drive high line                                                   |

| 26      | HRT       | Hardware Reset Timer pin (programmed with external capacitor and resistor)             |

| 27      | /SLEEP    | Sleep Mode & Power Down control                                                        |

| 28      | CS        | SPI chip select                                                                        |

| 29      | DI        | SPI serial data in                                                                     |

| 30      | SCLK      | SPI clock input                                                                        |

| 31      | DO        | SPI serial data out                                                                    |

| 32      | VREF3     | VDDH tracking linear regulator 3                                                       |

| 33      | VREF2     | VDDH tracking linear regulator 2                                                       |

| 34      | VDDH      | 5.0 V regulated supply output                                                          |

| 35      | VPRE_S    | Switching pre-regulator output sense                                                   |

| 36      | VPRE      | Switching pre-regulator output                                                         |

| 37      | VCOMP     | Switching pre-regulator compensation (error amplifier output)                          |

| 38      | INV       | Switching pre-regulator error amplifier inverting input                                |

| 39      | GND       | Ground                                                                                 |

| 40      | SW2G      | External power switch (MOSFET) gate drive — Boost regulator                            |

| 41      | воот      | Bootstrap capacitor                                                                    |

| 42      | SW1       | Source of the internal power switch (n–channel MOSFET)                                 |

| 43      | SW1       | Source of the internal power switch (n–channel MOSFET)                                 |

| 44      | SW1       | Source of the internal power switch (n-channel MOSFET)                                 |

NOTE: The exposed pad of the 44 HSOP package is electrically and thermally connected with the IC ground.

# PIN FUNCTION DESCRIPTION (44-QFN Package)

| PIN NO. | NAME      | DESCRIPTION                                                                            |

|---------|-----------|----------------------------------------------------------------------------------------|

| 1       | GND       | Ground                                                                                 |

| 2       | SW2G      | External power switch (MOSFET) gate drive — Boost Reg.                                 |

| 3       | воот      | Bootstrap capacitor                                                                    |

| 4       | SW1       | Source of the internal power switch (n-channel MOSFET)                                 |

| 5       | SW1       | Source of the internal power switch (n-channel MOSFET)                                 |

| 6       | SW1       | Source of the internal power switch (n-channel MOSFET)                                 |

| 7       | VBAT      | Battery supply to IC (external reverse battery protection needed in some applications) |

| 8       | VBAT      | Battery supply to IC (external reverse battery protection needed in some applications) |

| 9       | KA_VBAT   | Keep alive battery supply (with internal protection diode)                             |

| 10      | VIGN      | Turn on control through ignition switch (with internal protection diode)               |

| 11      | VKAM      | VDDL tracking Keep Alive Memory (Standby) supply                                       |

| 12      | VKAM_FB   | VKAM output feedback                                                                   |

| 13      | VSEN      | Switched battery output                                                                |

| 14      | REGON     | Regulator "Hold On" input                                                              |

| 15      | WAKEUP    | CAN wake up event output                                                               |

| 16      | VREF1     | VDDH tracking linear regulator 1                                                       |

| 17      | VPP_EN    | VPP enable                                                                             |

| 18      | VPP       | 5.0 V/ 3.3 V FLASH memory programming supply, tracking VDDH/VDD3_3                     |

| 19      | VDD3_3    | 3.3 V regulated supply output, base drive for optional external pass transistor        |

| 20      | VDD3_3FB  | VDD3_3 output feedback                                                                 |

| 21      | VDDL_X    | VDDL optional external pass transistor base drive, operating in Boost Mode only        |

| 22      | VDDL_B    | VDDL external pass transistor base drive                                               |

| 23      | VDDL_FB   | VDDL output feedback                                                                   |

| 24      | /PRERESET | Open drain /PRERESET output, occurs 0.7 us prior to /HRESET (Hardware Reset)           |

| 25      | /HRESET   | Open drain / HRESET (Hardware Reset) output                                            |

| 26      | /PORESET  | Open drain / PORESET (Power On Reset) supervising VKAM supply to the microprocessor.   |

| 27      | CANRXD    | CAN receive data (DOUT)                                                                |

| 28      | CANTXD    | CAN transmit data (DIN)                                                                |

| 29      | GND       | Ground                                                                                 |

| 30      | CANL      | CAN differential bus drive low line                                                    |

| 31      | CANH      | CAN differential bus drive high line                                                   |

| 32      | HRT       | Hardware Reset Timer pin (programmed with external capacitor and resistor)             |

| 33      | /SLEEP    | Sleep Mode & Power Down control                                                        |

| 34      | CS        | SPI chip select                                                                        |

| 35      | DI        | SPI serial data in                                                                     |

| 36      | SCLK      | SPI clock input                                                                        |

| 37      | DO        | SPI serial data out                                                                    |

| 38      | VREF3     | VDDH tracking linear regulator 3                                                       |

| 39      | VREF2     | VDDH tracking linear regulator 2                                                       |

| 40      | VDDH      | 5.0 V regulated supply output                                                          |

| 41      | VPRE_S    | Switching pre-regulator output sense                                                   |

| 42      | VPRE      | Switching pre–regulator output                                                         |

| 43      | VCOMP     | Switching pre-regulator compensation (error amplifier output)                          |

| 44      | INV       | Switching pre-regulator error amplifier inverting input                                |

NOTE: The exposed pad of the 44 QFN package is electrically and thermally connected with the IC ground.

### PIN FUNCTION DESCRIPTION (54 SOICW-EP Package)

| PIN NO.  | NAME      | DESCRIPTION                                                                                                            |

|----------|-----------|------------------------------------------------------------------------------------------------------------------------|

| 1        | GND       | Ground                                                                                                                 |

| 2        | CANL      | CAN differential bus drive low line                                                                                    |

| 3        | CANH      | CAN differential bus drive high line                                                                                   |

| 4        | HRT       | Hardware Reset Timer pin (programmed with external capacitor and resistor)                                             |

| 5        | /SLEEP    | Sleep Mode & Power Down control                                                                                        |

| 6        | N/C       | No Connect                                                                                                             |

| 7        | CS        | SPI chip select                                                                                                        |

| 8        | DI        | SPI serial data in                                                                                                     |

| 9        | SCLK      | SPI clock input                                                                                                        |

| 10       | DO        | SPI serial data out                                                                                                    |

| 11       | N/C       | No Connect                                                                                                             |

| 12       | VREF3     | VDDH tracking linear regulator 3                                                                                       |

| 13       | VREF2     | VDDH tracking linear regulator 2                                                                                       |

| 14       | VREF2     | 5.0 V regulated supply output                                                                                          |

| 15       | VPRE_S    | Switching pre–regulator output sense                                                                                   |

| 16       | VPRE_S    | Switching pre-regulator output                                                                                         |

|          |           |                                                                                                                        |

| 17<br>18 | VCOMP     | Switching pre–regulator compensation (error amplifier output)  Switching pre–regulator error amplifier inverting input |

|          |           | Ground                                                                                                                 |

| 19       | GND       |                                                                                                                        |

| 20       | SW2G      | External power switch (MOSFET) gate drive — Boost regulator                                                            |

| 21       | BOOT      | Bootstrap capacitor                                                                                                    |

| 23       | SW1       | Source of the internal power switch (n-channel MOSFET)                                                                 |

| 24       | SW1       | Source of the internal power switch (n-channel MOSFET)                                                                 |

| 25       | SW1       | Source of the internal power switch (n-channel MOSFET)                                                                 |

| 26       | SW1       | Source of the internal power switch (n–channel MOSFET)                                                                 |

| 27       | SW1       | Source of the internal power switch (n–channel MOSFET)                                                                 |

| 28       | VBAT      | Battery supply to IC (external reverse battery protection needed in some applications)                                 |

| 29       | VBAT      | Battery supply to IC (external reverse battery protection needed in some applications)                                 |

| 30       | VBAT      | Battery supply to IC (external reverse battery protection needed in some applications)                                 |

| 31       | VBAT      | Battery supply to IC (external reverse battery protection needed in some applications)                                 |

| 32       | VBAT      | Battery supply to IC (external reverse battery protection needed in some applications)                                 |

| 33       | KA_VBAT   | Keep alive supply (with internal protection diode)                                                                     |

| 34       | N/C       | No Connect                                                                                                             |

| 35       | VIGN      | Turn–On control through ignition switch (with internal protection diode)                                               |

| 36       | VKAM      | VDDL tracking Keep Alive Memory (Standby) supply                                                                       |

| 37       | VKAM_FB   | VKAM output feedback                                                                                                   |

| 38       | VSEN      | Switched battery output                                                                                                |

| 39       | REGON     | Regulator "Hold On" input                                                                                              |

| 40       | WAKEUP    | CAN wake up event output                                                                                               |

| 41       | VREF1     | VDDH tracking linear regulator 1                                                                                       |

| 42       | VPP_EN    | VPP enable                                                                                                             |

| 43       | VPP       | 5.0 V/ 3.3 V FLASH memory programming supply, tracking VDDH/VDD3_3                                                     |

| 44       | VDD3_3    | 3.3 V regulated supply output, base drive for optional external pass transistor                                        |

| 45       | VDD3_3FB  | VDD3_3 output feedback                                                                                                 |

| 46       | VDDL_X    | VDDL optional external pass transistor base drive, operating in Boost Mode only                                        |

| 47       | VDDL_B    | VDDL external pass transistor base drive                                                                               |

| 48       | VDDL_FB   | VDDL output feedback                                                                                                   |

| 49       | N/C       | No Connect                                                                                                             |

| 50       | /PRERESET | Open drain /PRERESET output, occurs 0.7 us prior to /HRESET (Hardware Reset)                                           |

| 51       | /HRESET   | Open drain / HRESET (Hardware Reset) output                                                                            |

| 52       | /PORESET  | Open drain / PORESET (Power On Reset) supervising VKAM supply to the microprocessor.                                   |

| 53       | CANRXD    | CAN receive data (DOUT)                                                                                                |

| 54       | CANTXD    | CAN transmit data (DIN)                                                                                                |

NOTE: The exposed pad of the 54 SOICW-EP package is electrically and thermally connected with the IC ground.

#### 1. MAXIMUM RATINGS (Maximum Ratings indicate sustained limits beyond which damage to the device may occur.

Voltage parameters are absolute voltages referenced to ground.)

| Parameter                                                                                                            |                                  | Min.         | Max.              | Unit        |

|----------------------------------------------------------------------------------------------------------------------|----------------------------------|--------------|-------------------|-------------|

| Supply Voltage (VBAT), Load Dump                                                                                     |                                  | -0.3         | +45               | V           |

| Supply Voltage (KA_VBAT, VIGN), Load Dump                                                                            |                                  | -18          | +45               | V           |

| Supply Voltages (VDDH, VPP, VDD3_3, VDDL, VKAM)                                                                      |                                  | -0.3         | +5.8              | V           |

| Supply Voltages (VREF1, VREF2, VREF3, VSEN)                                                                          |                                  | -2.0         | +18               | V           |

| CANL, CANH (0 <vbat<18 limit)<="" no="" td="" time="" vdc=""><td></td><td>-18</td><td>+26.5</td><td>V</td></vbat<18> |                                  | -18          | +26.5             | V           |

| ESD Voltage Human Body Model all pins Machine Model all pins                                                         | (Note 1)<br>(Note 2)             | -2.0<br>-200 | +2.0<br>+200      | kV<br>V     |

| CANLesd, CANHesd                                                                                                     | (Note 1)                         | -4.0         | +4.0              | kV          |

| CANLesd, CANHesd                                                                                                     | (Note 2)                         | -200         | +200              | V           |

| CANLtransient, CANHtransient                                                                                         | (Note 3)                         | -200         | +200              | V           |

| /SLEEP                                                                                                               |                                  | -18          | +45               | V           |

| REGON, VPP_EN, /HRESET, /PORESET, /PRERESET, HRT, DO, DI, CS, SCLK                                                   |                                  | -0.3         | +7.0              | V           |

| CANTXD, CANRXD                                                                                                       |                                  | -0.3         | +7.0              | V           |

| Operational Package Temperature [Ambient Temperature]                                                                |                                  | -40          | +125              | °C          |

| Storage Temperature                                                                                                  |                                  | -65          | +150              | °C          |

| Power Dissipation ( $T_A = 125$ °C)<br>44 HSOP<br>44 QFN<br>54 SOICW–EP                                              | (Note 4)<br>(Note 4)<br>(Note 4) |              | 8.3<br>5.0<br>5.0 | W<br>W<br>W |

| Lead Soldering Temperature                                                                                           | (Note 5)                         |              | 260               | °C          |

| Maximum Junction Temperature                                                                                         |                                  |              | +150              | °C          |

| R <sub>0</sub> JA, Thermal Resistance, Junction to Ambient (44 HSOP)                                                 | (Note 6)                         |              | 41                | °C/W        |

| R <sub>0</sub> JC, Thermal Resistance, Junction to Case (44 HSOP)                                                    | (Note 7)                         |              | 0.2               | °C/W        |

| R <sub>0</sub> JB, Thermal Resistance, Junction to Base (44 HSOP)                                                    | (Note 8)                         |              | 3                 | °C/W        |

| R <sub>0</sub> JA, Thermal Resistance, Junction to Ambient (44 QFN)                                                  | (Note 6)                         |              | 77                | °C/W        |

| R <sub>0</sub> JC, Thermal Resistance, Junction to Case (44 QFN)                                                     | (Note 7)                         |              | 1.7               | °C/W        |

| $R_{	heta JB}$ , Thermal Resistance, Junction to Base (44 QFN)                                                       | (Note 8)                         |              | 5.0               | °C/W        |

| R <sub>0</sub> JA, Thermal Resistance, Junction to Ambient (54 SOICW–EP)                                             | (Note 6)                         |              | 52                | °C/W        |

| $R_{	heta JC}$ , Thermal Resistance, Junction to Case (54 SOICW–EP)                                                  | (Note 7)                         |              | 1.2               | °C/W        |

| R <sub>θJB</sub> , Thermal Resistance, Junction to Base (54 SOICW–EP)                                                | (Note 8)                         |              | 8.1               | °C/W        |

- 1. Human body model: C = 100 pF,  $R = 1.5 \text{ k}\Omega$ .

- 2. Machine model: C = 200 pF,  $R = 10 \Omega$  and  $L = 0.75 \mu H$ . In case of a discharge from pin CANL to pin GND: -100 V < CANL transient < +100 V; in case of a discharge from pin CANH to Vcc: -150 V < CANH transient < +150 V.

- 3. The waveforms of the applied transients is in accordance with "ISO 7637 part 1" test pulses 1, 2, 3a and 3b.

- 4. Maximum power dissipation at indicated junction temperature.

- 5. Lead soldering temperature limit is for 10 seconds maximum duration; contact Motorola Sales Office for device immersion soldering time/temperature limits.

- 6. Thermal resistance measured in accordance with EIA/JESD51-2.

- 7. Theoretical thermal resistance from the die junction to the exposed pad.

- 8. Thermal resistance measured in accordance with JESD51-8.

#### 2. RECOMMENDED OPERATING CONDITIONS (All voltages are with respect to ground unless otherwise noted)

| Parameter                                                        | Value       | Unit |

|------------------------------------------------------------------|-------------|------|

| Supply Voltages (VBAT, KA_VBAT)                                  | 4.0 to 26.5 | V    |

| Switching Regulator Output Current (I <sub>VPRE</sub> ) (Note 1) | 0 to 1.2    | A    |

| VDDH Output Current                                              | 0 to 400    | mA   |

| VDD3_3 Output Current                                            | 0 to 120    | mA   |

| VDDL_B Pass Transistor Base Drive Current                        | 0 to 40     | mA   |

| VPP Output Current                                               | 0 to 150    | mA   |

| VREF Output Current                                              | 0 to 100    | mA   |

| VSEN Output Current                                              | 0 to 125    | mA   |

| VKAM Standby Output Current (normal mode of operation)           | 0 to 60     | mA   |

| VKAM Standby Output Current (standby mode of operation)          | 0 to 12     | mA   |

<sup>1.</sup> See Typical Application Diagram in Figure 1.

| Characteristic                                                                                                                      | Symbol                             | Min.       | Тур.        | Max.       | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------|-------------|------------|------|

| DC CHARACTERISTICS:<br>GENERAL                                                                                                      |                                    |            |             |            |      |

| Start Up Voltage                                                                                                                    | VBAT <sub>start</sub>              |            |             | 6.2        | V    |

| Power Dissipation, VBAT = 13.3 V (Buck Mode)                                                                                        |                                    |            | 1.8         |            | W    |

| Undervoltage Shut Down                                                                                                              | VBATUV                             | 3.4        |             | 3.9        | V    |

| Battery Input Current, Power Down Mode, VIGN = 0 V; REGON = 0 V;<br>I <sub>VKAM</sub> = 0 mA, VBAT = 13.3 V; Battery Voltage = 14 V | IVBAT(sleep)                       |            | 750         | 1000       | μА   |

| Battery Input Current, Keep Alive Mode<br>VIGN = 0; I <sub>VKAM</sub> = −10 mA                                                      |                                    |            |             | 12         | mA   |

| Power On Current, Regulator ON with no load on VDDH, VDD3_3, VDDL, VKAM, VREF, VPP, VSEN; VBAT = 13.3 V                             | IVBAT(no load)                     |            |             | 27         | mA   |

| Battery Input Current, VPRE = -1.0 A, VBAT = 4.5 V                                                                                  | I <sub>VBAT(4.5)</sub>             |            | 2.2         | 3.0        | А    |

| Battery Input Current, VPRE = -1.0 A, VBAT = 9 V                                                                                    | IVBAT(9)                           |            |             | 1.5        | А    |

| Battery Input Current, VPRE = -1.0 A, VBAT = 13.3 V                                                                                 | IVBAT(13.3)                        |            |             | 1.2        | А    |

| Battery Input Current, VPRE = -1.0 A, VBAT = 18 V                                                                                   | IVBAT(18)                          |            |             | 1.1        | Α    |

| MODE CONTROL                                                                                                                        |                                    |            |             |            |      |

| VIGN Input Voltage Threshold, REGON = 0 V<br>VBAT = 13.3 V; Battery Voltage = 14 V                                                  | V <sub>IH</sub><br>V <sub>IL</sub> | 2.8<br>1.7 | 3.15<br>2.0 | 3.4<br>2.3 | V    |

| VIGN Hysteresis                                                                                                                     |                                    | 0.7        | 1.0         | 1.5        | V    |

| VIGN Pull-Down Current, REGON = 0V<br>VBAT = 13.3 V, Battery Voltage = 14 V, VIGN = 14 V                                            | R <sub>PD</sub>                    | 40         | 100         | 150        | μА   |

| REGON Input High Voltage Threshold                                                                                                  | VIH                                | 1.3        | 1.65        | 2.1        | V    |

| REGON Input Low Voltage Threshold                                                                                                   | VIL                                | 0.8        | 1.35        | 1.5        | V    |

| REGON Input Voltage Threshold Hysteresis                                                                                            | V <sub>Ihys</sub>                  | 0.2        | 0.3         | 0.4        | V    |

| REGON Pull-Down Current, REGON = VDDH to V <sub>IL(min)</sub>                                                                       | R <sub>PD</sub>                    | 10         | 20          | 50         | μΑ   |

| /SLEEP Input High Voltage Threshold                                                                                                 | VIH                                | 1.7        | 2.2         | 2.6        | V    |

| /SLEEP Input Low Voltage Threshold                                                                                                  | V <sub>IL</sub>                    | 1.4        | 1.9         | 2.2        | V    |

| /SLEEP Input Voltage Threshold Hysteresis                                                                                           | V <sub>Ihys</sub>                  | 0.2        | 0.3         | 0.4        | V    |

| /SLEEP Pull-Down Current, /SLEEP = VDDH to V <sub>IL(min)</sub>                                                                     | R <sub>PD</sub>                    | 10         | 20          | 50         | μΑ   |

| VPP_EN Input High Voltage Threshold                                                                                                 | VIH                                | 1.3        | 1.65        | 2.1        | V    |

| VPP_EN Input Voltage Low Threshold                                                                                                  | VIL                                | 0.8        | 1.35        | 1.5        | V    |

| VPP_EN Pull-Down Current, VPP_EN = VDDH to V <sub>IL(min)</sub>                                                                     | R <sub>PD</sub>                    | 10         | 20          | 50         | μА   |

| Characteristic                                                            |           | Symbol              | Min.  | Тур. | Max. | Unit |

|---------------------------------------------------------------------------|-----------|---------------------|-------|------|------|------|

| DC CHARACTERISTICS:                                                       |           |                     |       |      |      |      |

| BUCK CONVERTER                                                            |           |                     |       |      |      |      |

| Buck Converter Output Voltage, VBAT = 7.5V to 18V; ILC                    | OAD=500mA | VPRE                | 5.4   | 5.6  | 5.8  | V    |

| Buck to Boost Mode Threshold Voltage                                      | (Note 1)  | VBAT <sub>thd</sub> |       | 6.7  |      | V    |

| Boost to Buck Mode Threshold Voltage                                      | (Note 1)  | VBAT <sub>thu</sub> |       | 7.2  |      | V    |

| N-channel power MOSFET SW1                                                |           |                     | •     | •    | •    | •    |

| SW1 Drain–Source Breakdown Voltage                                        | (Note 1)  | BVDSS               | 50    |      |      | V    |

| SW1 Continuous Drain Current                                              |           | ID <sub>SW1</sub>   | -2.75 |      |      | А    |

| SW1 Drain-Source Current Limit                                            |           | IscSW1              | -2.5  | -3.0 | -3.5 | А    |

| SW1 Drain–Source On–Resistance; I <sub>D</sub> = 1.0 A, VBAT = 9          | 9.0 V     | R <sub>DS(on)</sub> |       |      | 300  | mΩ   |

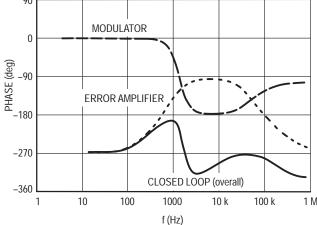

| Error Amplifier (Design Information Only)                                 |           | , ,                 | •     |      | •    | •    |

| Input Offset Voltage                                                      | (Note 1)  | Vos                 |       | 20   |      | mV   |

| DC Open Loop Gain                                                         | (Note 1)  | AVOL                |       | 80   |      | dB   |

| Unity Gain Bandwidth                                                      | (Note 1)  | BW                  |       | 1.5  |      | MHz  |

| Output Voltage Swing — High Level                                         | (Note 1)  | VOH                 |       | 4.2  |      | V    |

| Output Voltage Swing — Low Level                                          | (Note 1)  | V <sub>OL</sub>     |       | 0.4  |      | V    |

| Output Source Current                                                     | (Note 1)  | lout                |       | 1.0  |      | mA   |

| Output Sink Current                                                       | (Note 1)  | lout                |       | 200  |      | μА   |

| Ramp Generator                                                            | '         |                     | •     |      | •    | •    |

| Sawtooth Peak Voltage                                                     | (Note 1)  | Vosc                |       |      | 3.5  | V    |

| Sawtooth Peak-to-Peak Voltage                                             | (Note 1)  | Voscp-p             |       |      | 3.0  | V    |

| BOOST CONVERTER                                                           | ,         |                     | •     | •    | •    | •    |

| External Power MOSFET Gate Drive SW2G                                     |           |                     |       |      |      |      |

| Boost Converter Output Voltage, VBAT = $4.5 \text{ V}$ to $6.0 \text{ V}$ | (Note 1)  | VPRE                | 5.9   | 6.0  | 6.6  | V    |

| SW2G Output Voltage, Power MOSFET On                                      | (Note 1)  | Vg                  |       | VPRE |      | V    |

| SW2G Source Continuous Current                                            | (Note 1)  | I <sub>source</sub> |       | TBD  |      | mA   |

| SW2G Sink Continuous Current                                              |           | I <sub>sink</sub>   | 200   | 300  | 400  | mA   |

| AC CHARACTERISTICS:                                                       |           |                     |       |      |      |      |

| BUCK CONVERTER                                                            |           |                     |       |      |      |      |

| Oscillator Frequency                                                      |           | Freq                | 180   | 200  | 220  | kHz  |

| SW1 Switch Turn-ON Time                                                   | (Note 1)  | t <sub>T</sub> –ON  |       | TBD  |      | ns   |

| SW1 Switch Turn-OFF Time                                                  | (Note 1)  | tT-OFF              |       | TBD  |      | ns   |

| SW2G Switch Turn–ON Time, C <sub>gate</sub> = pF                          | (Note 1)  | t <sub>T</sub> ON   |       | TBD  |      | ns   |

| SW2G Switch Turn-OFF Time, C <sub>gate</sub> = pF                         | (Note 1)  | tT-OFF              |       | TBD  |      | ns   |

| OFF Time                                                                  | (Note 1)  | <sup>t</sup> OFF    |       | 1.25 |      | μs   |

| Duty cycle                                                                | (Note 1)  | d                   |       | 75   |      | %    |

<sup>1.</sup> Guaranteed by design but not production tested.

| ondate oder igare i, amode etherwide hotea.)                                                         |                           |       |       |             |      |

|------------------------------------------------------------------------------------------------------|---------------------------|-------|-------|-------------|------|

| Characteristic                                                                                       | Symbol                    | Min.  | Тур.  | Max.        | Unit |

| DC CHARACTERISTICS:                                                                                  |                           |       |       |             |      |

| VDDH                                                                                                 |                           |       |       |             |      |

| VDDH Output Voltage, I <sub>VDDH</sub> = -400 mA;                                                    | VDDH                      | 4.9   | 5.0   | 5.1         | V    |

| VDDH Load Regulation, VBAT = 13.3 V; I <sub>VDDH</sub> = 0 to -400 mA;                               | LoadRgVDDH                | -40   |       | 40          | mV   |

| VDDH Line Regulation, VBAT = $4.0 \text{ V}$ to $26.5 \text{ V}$ ; $I_{VDDH} = -400 \text{ m/s}$     | A; LineRgVDDH             | -20   |       | 20          | mV   |

| VDDH Drop Out Voltage, VPRE – VDDH, I <sub>VDDH</sub> = –400 mA; Decrease VBAT until Resets asserted | V <sub>DOV</sub>          |       |       | 450         | mV   |

| VDDH Output Current, VBAT = 4.0 V to 26.5 V                                                          | IVDDH                     |       | -400  |             | mA   |

| VDDH Short Circuit Current, VDDH = 0 V                                                               | Isc                       | -750  |       | -440        | mA   |

| VDDH Maximum Allowed Feedback Current (Note 2) (Power Up Sequence Guaranteed) (Note 2)               | ·                         |       |       | 135         | μА   |

| VDDH Reset Voltage, Range of VDDH where Resets must remain asserted                                  | VVDDH_HRST                | 0.5   |       | 4.8         | V    |

| Thermal Shutdown Junction Temperature (Note                                                          | I) TS <sub>DIS</sub>      | 150   |       | 190         | °C   |

| Thermal Shutdown Hysteresis (Note                                                                    |                           | 5.0   |       | 20          | °C   |

| VDD3_3                                                                                               |                           |       | 1     | 1           | 1    |

| VDD3_3 Output Voltage, I <sub>VDD3_3</sub> = -120 mA;                                                | VDD3_3                    | 3.21  | 3.3   | 3.36        | V    |

| VDD3_3 Load Regulation, VBAT = 13.3 V; I <sub>VDD3_3</sub> = 0 to -120 m                             | A LoadRg <sub>VDD3</sub>  | -40   |       | 40          | mV   |

| VDD3_3 Line Regulation, VBAT = 4.0V to 26.5V; I <sub>VDD3_3</sub> = -120i                            | mA LineRg <sub>VDD3</sub> | -20   |       | 20          | mV   |

| VDD3_3 Drop Out Voltage, VPRE – VDD3_3 IVDD3_3 = -120 mA; Decrease VBAT until Resets asserted        | VDOV                      |       |       | 2.04        | V    |

| VDD3_3 Output Current, VBAT = 4.0 V to 26.5 V                                                        | I <sub>VDD3_3</sub>       |       | -120  |             | mA   |

| VDD3_3 Short Circuit Current, VDD3_3 = 0 V                                                           | ISC                       | -320  |       | -130        | mA   |

| VDD3_3 Maximum Allowed Feedback Current (Note 2) (Power Up Sequence Guaranteed) (Note 2)             | 1)                        |       |       | 135         | μА   |

| VDD3_3 Reset Voltage<br>Range of VDD3_3 where Resets must remain asserted                            | VVDD3_HRST                | 0.5   |       | 3.1         | V    |

| Thermal Shutdown Junction Temperature (Note                                                          | I) TS <sub>DIS</sub>      | 150   |       | 190         | °C   |

| Thermal Shutdown Hysteresis (Note                                                                    |                           | 5.0   |       | 20          | °C   |

| VDDL                                                                                                 |                           |       |       | 1           | 1    |

| VDDL Feedback Reference Voltage, pin VDDL_FB IVDDL_B = 0 to -40 mA                                   | VDDL <sub>REF</sub>       | 1.242 | 1.267 | 1.292       | V    |

| VDDL Load Regulation, VBAT = 13.3 V; I <sub>VDDL_B</sub> = 0 to -40 mA                               | LoadRg <sub>VDDL</sub>    | -1.6  |       | 0           | %    |

| VDDL Line Regulation VBAT = 4.0 V to 26.5 V; IVDDL_B = -40 mA                                        | LineRgVDDL                | -0.8  |       | 0.8         | %    |

| VDDL Drop Out Voltage, VPRE – VDDL  IVDDL = –400 mA; VBAT decreases until Resets asserted            | VDOV                      |       |       | 1.3         | V    |

| VDDL Reset Voltage, Range of VDDL where Resets must remain asserted                                  | ) VVDDL_HRST              | 0.5   |       | VDDL<br>-5% | V    |

| VDDL Susceptibility to Feeding Back (Note 3 (Power Up Sequence Guaranteed)                           | 3) VDDL <sub>REF</sub>    |       |       | 0.187       | V    |

| VDDL_B Drive Output Current, VBAT = 7.5V to 26.5V                                                    | I <sub>VDDL_B</sub>       |       | -40   |             | mA   |

| VDDL_B Drive Short Circuit Current<br>VDDL_B = 0V, VBAT = 7.5V to 26.5V                              | IscVDDL_B                 | -100  |       | -45         | mA   |

| VDDL_X Drive Output Current, VBAT = 4.0 V to 6 V                                                     | I <sub>VDDL_B</sub>       |       | -40   |             | mA   |

| VDDL_X Drive Short Circuit Current, VDDL_X = 0V, VBAT = 4.0V                                         |                           | -100  |       | -45         | mA   |

| VDDL Feedback VDDL_FB Input Current, VDDL_FB = 5.0 V                                                 | I <sub>VDDL_FB</sub>      | 0     |       | 2.0         | μА   |

- 1. Guaranteed by design but not production tested.

- 2. Maximum allowed current flowing back into the regulator output.

- 3. Voltage fed back into the VDDL output, which still guaranties proper Power Up sequencing.

3. ELECTRICAL CHARACTERISTICS ( $-40^{\circ}C \le T_{\mbox{A}} \le +125^{\circ}C$ ; +4.0 V  $\le$  VBAT  $\le$  +26.5 V using the 33394 typical application circuit – see Figure 1, unless otherwise noted.)

| Characteristic                                                                                                                                                  | Symbol                 | Min.  | Тур.  | Max.        | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------|-------|-------------|------|

| DC CHARACTERISTICS:<br>VKAM                                                                                                                                     |                        |       |       |             |      |

| VKAM Feedback Reference Voltage, pin VKAM_FB Normal Mode (switcher running), I <sub>VKAM</sub> = 0 to -50mA                                                     | VKAM <sub>REF</sub>    | 1.242 | 1.267 | 1.292       | V    |

| VKAM Load Regulation, VBAT = 13.3 V; I <sub>VKAM</sub> = -0 to -50 mA                                                                                           | LoadRg <sub>VKAM</sub> | -1.6  |       | 0           | %    |

| VKAM Line Regulation, VBAT = 4.0 V to 26.5 V; I <sub>VKAM</sub> = -50 mA                                                                                        | LineRg <sub>VKAM</sub> | -0.8  |       | 0.8         | %    |

| VKAM Tracking to VDDL Voltage, VDDL – VKAM VBAT = 4.0 V to 26.5 V; $I_{VKAM}$ = 0 to –50 mA, $I_{VDDL}$ = 0 to –400mA                                           | VTVKAM                 | -1.6  |       | 0.8         | %    |

| VKAM Feedback Voltage — Power Down Mode<br>3.0 V ≤ Battery Voltage ≤ 26.5 V, I <sub>VKAM</sub> = −12 mA                                                         | VKAM                   | 0.675 |       |             | V    |

| VKAM Reset Voltage (/PORESET)<br>Range of VKAM where Resets must remain asserted                                                                                | VVKAM_HRST             | 0.5   |       | VKAM<br>-5% | V    |

| VKAM Output Current (Normal Mode), VBAT = 4.0 V to 26.5 V                                                                                                       | IVKAM                  |       | -50   |             | mA   |

| VKAM Output Current (Sleep Mode and when VBAT ≤ 4.0 V)                                                                                                          | IVKAM(sleep)           |       | -12   |             | mA   |

| VKAM Short Circuit Current, VKAM = 0 V                                                                                                                          | Isc                    | -140  |       | -50         | mA   |

| VKAM Feedback VKAM_FB Input Current, VKAM_FB = 5.0 V                                                                                                            | IVKAM_FB               | 0     |       | 2.0         | μΑ   |

| VKAM Output Capacitance Required, Capacitor Initial Tolerance 10%                                                                                               |                        | 22    |       | 100         | μF   |

| VPP                                                                                                                                                             |                        |       |       |             |      |

| VPP 5.0V Output Voltage (Default), $I_{VPP} = -150 \text{ mA}$                                                                                                  | VPP <sub>5</sub>       | 4.86  | 5.0   | 5.12        | V    |

| VPP 3.3 V Output Voltage (Programmed by SPI) $I_{VPP} = -150 \text{ mA}$                                                                                        | VPP <sub>3</sub>       | 3.22  | 3.3   | 3.38        | V    |

| VPP Load Regulation, VBAT = $13.3 \text{ V}$ ; $I_{VPP} = 0 \text{ to } -150 \text{ mA}$                                                                        | LoadRg <sub>VPP</sub>  | -0.8  |       | 0.8         | %    |

| VPP Line Regulation, VBAT = $4.0 \text{ V}$ to $26.5 \text{ V}$ ; $I_{VPP} = -150 \text{ mA}$                                                                   | LineRg <sub>VPP</sub>  | -0.4  |       | 0.4         | %    |

| VPP Tracking to VDDH Voltage, VDDH – VPP, VBAT = $4.0 \text{ V}$ to $26.5 \text{ V}$ ; $I_{VPP} = 0$ to $-150 \text{ mA}$ ; $I_{VDDH} = 0$ to $-400 \text{ mA}$ | VT <sub>VPP</sub>      | -0.8  |       | 0.8         | %    |

| VPP Drop Out Voltage, VPRE — VPP (VPP set to default 5.0V) IVPP = -150 mA; Decrease VBAT until VPP is out of specification (less than 4.86 V)                   | VDOV                   |       |       | 0.4         | V    |

| VPP Output Current, VBAT = 4.0 V to 26.5 V                                                                                                                      | IVPP                   |       | -150  |             | mA   |

| VPP Short Circuit Current, VPP = 0 V                                                                                                                            | Isc                    | -360  |       | -165        | mA   |

| Thermal Shutdown Junction Temperature (Note 1)                                                                                                                  | TS <sub>DIS</sub>      | 150   |       | 190         | °C   |

| Thermal Shutdown Hysteresis (Note 1)                                                                                                                            | TSHYS                  | 5.0   |       | 20          | °C   |

<sup>1.</sup> Guaranteed by design but not production tested.

| Characteristic                                                                                                                               | Symbol                     | Min. | Тур. | Max. | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------|------|------|------|

| DC CHARACTERISTICS:                                                                                                                          |                            |      | •    |      |      |

| VREF1, 2, 3                                                                                                                                  |                            |      |      |      |      |

| VREF Output Voltage, I <sub>VREF</sub> = −100 mA                                                                                             | VREF                       | 4.86 | 5.0  | 5.12 | V    |

| VREF Load Regulation, VBAT = 13.3 V; I <sub>VREF</sub> = 0 to −100 mA                                                                        | LoadRgVREF                 | -40  |      | 40   | mV   |

| VREF Line Regulation, VBAT = $4.0 \text{ V}$ to $26.5 \text{ V}$ ; $I_{VREF} = -100 \text{ mA}$                                              | LineRgVREF                 | -20  |      | 20   | mV   |

| VREF Tracking to VDDH Voltage, VDDH – VREF,<br>VBAT = 4.0 V to 26.5 V, I <sub>VREF</sub> = 0 to –100 mA;<br>I <sub>VDDH</sub> = 0 to –400 mA | VT <sub>VREF</sub>         | -40  |      | 20   | mV   |

| VREF Drop Out Voltage, VPRE–VREF IVREF = -100 mA; Decrease VBAT until VREF is out of specification (less than 4.86 V)                        | on VDOV                    |      |      | 0.4  | V    |

| VREF Output Current, VBAT = 4.0 V to 26.5 V                                                                                                  | IVREF                      |      | -100 |      | mA   |

| VREF Short Circuit Current, VREF = −2.0 V                                                                                                    | Isc                        | -260 |      | -110 | mA   |

| VREF Short to Battery Load Current, VBAT = 18 V, VREF = 18 V                                                                                 | IstbyreF                   |      |      | 40   | mA   |

| VREF Leakage Current, VREF disabled, VREF = -2.0 V                                                                                           | ILKVREF                    | -2.0 |      |      | mA   |

| Thermal Shutdown Junction Temperature (Note                                                                                                  | ) TS <sub>DIS</sub>        | 150  |      | 190  | °C   |

| Thermal Shutdown Hysteresis (Note                                                                                                            | I) TS <sub>HYS</sub>       | 5.0  |      | 20   | °C   |

| VSEN                                                                                                                                         |                            |      |      |      |      |

| VSEN Saturation Voltage, I <sub>VSEN</sub> = 0 to -125 mA, VBAT= 8 to 16 \                                                                   | / VSEN <sub>sat</sub>      |      |      | 0.2  | V    |

| VSEN Output Voltage Limit, I <sub>VSEN</sub> = 0 to -125mA, VBAT= 16 to 26                                                                   | 5.5V VSEN <sub>limit</sub> | 16   | 17   | 21   | V    |

| VSEN Short Circuit Current, VSEN = -2.0 V                                                                                                    | Iscvsen                    | -290 |      | -140 | mA   |

| VSEN Short to Battery Load Current, VBAT = 18 V, VSEN = 18 V                                                                                 | Istbysen                   |      |      | 40   | mA   |

| VSEN Leakage Current, VSEN disabled, VSEN = −2.0 V                                                                                           | ILKVSEN                    |      |      | 200  | μΑ   |

| Thermal Shutdown Junction Temperature (Note                                                                                                  | ) TS <sub>DIS</sub>        | 150  |      | 190  | °C   |

| Thermal Shutdown Hysteresis (Note                                                                                                            | I) TS <sub>HYS</sub>       | 5.0  |      | 20   | °C   |

<sup>1.</sup> Guaranteed by design but not production tested.

| Characteristic                                                                                                   | Symbol | Min.     | Тур. | Max. | Unit |

|------------------------------------------------------------------------------------------------------------------|--------|----------|------|------|------|

| DC CHARACTERISTICS:                                                                                              |        |          |      |      |      |

| SUPERVISORY OUTPUTS                                                                                              |        |          |      |      |      |

| Reset Voltage Thresholds<br>/HRESET to follow /PRERESET by 0.7 μs                                                |        |          |      |      |      |

| VDDH Reset Upper Threshold Voltage (Note 1)                                                                      |        |          |      | 5.2  | V    |

| VDDH Reset Lower Threshold Voltage (Note 1)                                                                      |        | 4.8      |      |      | V    |

| VDD3_3 Reset Upper Threshold Voltage (Note 1)                                                                    |        |          |      | 3.43 | V    |

| VDD3_3 Reset Lower Threshold Voltage (Note 1)                                                                    |        | 3.17     |      |      | V    |

| VDDL Reset Upper Threshold Voltage (Notes 1, 4)                                                                  |        |          |      | 1.35 | V    |

| VDDL Reset Lower Threshold Voltage (Notes 1, 4)                                                                  |        | 1.2      |      |      | V    |

| /PORESET Voltage Threshold                                                                                       | •      |          |      |      |      |

| VKAM Reset Upper Threshold Voltage (Notes 2, 5)                                                                  |        |          |      | 1.35 | V    |

| VKAM Reset Lower Threshold Voltage (Notes 2, 5)                                                                  |        | 1.2      |      |      | V    |

| /PRERESET, /HRESET, /PORESET Open Drain Maximum Voltage (Note 3)                                                 |        |          |      | 7.0  | V    |

| /PRERESET, /HRESET, /PORESET Open Drain Pull–Down Current, $V_{\text{reset}} < 0.4 \text{ V}$                    |        |          |      | 1.0  | mA   |

| /PRERESET, /HRESET, /PORESET Low-Level Output Voltage, IOL = 1.0 mA                                              |        |          |      | 0.5  | V    |

| /PRERESET /HRESET /PORESET Leakage Current                                                                       |        |          |      | 15   | μА   |

| WAKEUP High–Level Output Voltage, IOH = -800μA                                                                   |        | VDDH-0.8 |      |      | V    |

| WAKEUP Low-Level Output Voltage, IOL = 1.6 mA                                                                    |        |          |      | 0.4  | V    |

| HRT Voltage Threshold                                                                                            |        | 2.49     | 2.53 | 2.57 | V    |

| HRT Sink Current                                                                                                 |        |          |      | 1.0  | mA   |

| HRT Leakage Current                                                                                              |        |          |      | 5.0  | μА   |

| HRT Saturation Voltage, HRT Current = 1 mA                                                                       |        |          |      | 0.4  | V    |

| AC CHARACTERISTICS:                                                                                              |        |          |      |      |      |

| SUPERVISORY OUTPUTS                                                                                              |        |          |      |      |      |

| /PORESET Delay Delay time from VKAM in regulation and stable to the release of /PORESET                          |        | 7.0      | 10   | 15   | ms   |

| Reset Delay Time Time from fault on VDDH, VDD3_3, VDDL or VKAM to Reset (/PORESET, /PRERESET)                    |        | 10       | 20   | 50   | μs   |

| /HRESET Delay Time<br>Time From /PRERESET low to /HRESET low                                                     |        | 0.5      | 0.7  | 1.0  | μs   |

| VDDH, VDDL, VREF Power Up Sequence Max Power Up Sequence Time Dependent on Output Load Characteristics. (Note 3) |        | 800      |      |      | μs   |

#### NOTF:

- 1. VDDH, VDD3 $\_$ 3, VDDL regulator outputs supervised by <code>/PRERESET</code> and <code>/HRESET</code>.

- 2. VKAM regulator output supervised by /PORESET.

- 3. Guaranteed by design but not production tested.

- 4. Measured at the VDDL\_FB pin.

- 5. Measured at the VKAM\_FB pin.

| Characteristic                                                                                         | Symbol                | Min.         | Тур. | Max. | Unit |

|--------------------------------------------------------------------------------------------------------|-----------------------|--------------|------|------|------|

| DC CHARACTERISTICS:                                                                                    |                       |              |      |      |      |

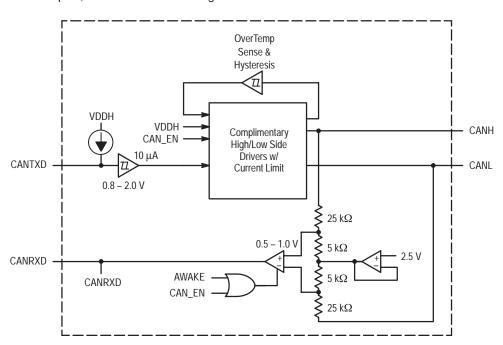

| <b>CAN Transceiver</b> (Bus Load CANH to CANL $R_L = 60 \Omega$ ; Vdiff = $V_C$                        | CANH - VCANL)         |              |      |      |      |

| CAN Transceiver Supply Current (dominant), V <sub>CANTXD</sub> = 0V                                    | IDD(CAN)              | 30           | 50   | 70   | mA   |

| CAN Transceiver Supply Current (recessive), VCANTXD = VDDH                                             | I <sub>DD</sub> (CAN) | 2.5          | 5    | 10   | mA   |

| Transmitter Data Input CANTXD                                                                          | (- /                  |              |      |      |      |

| High-Level Input Voltage Threshold (recessive), Vdiff<0.5V                                             | VIH                   | 1.4          |      | 2.0  | V    |

| Low-Level Input Voltage Threshold (dominant), Vdiff>1.0V                                               | V <sub>IL</sub>       | 0.8          |      | 1.4  | V    |

| High-Level Input Current, VCANTXD = VDDH                                                               | lін                   | -5           | 0    | +5   | μΑ   |

| Low-Level Input Current, V <sub>CANTXD</sub> = 0V                                                      | I <sub>IL</sub>       | -10          | -15  | -30  | μΑ   |

| CANTXD Pull-up Current, V <sub>CANTXD</sub> = 0V to V <sub>IH(max)</sub>                               | I <sub>PU</sub>       | -10          |      | -60  | μΑ   |

| CANTXD Input Capacitance (Note 1                                                                       | _                     |              | 5    | 10   | pF   |

| Receiver Data Output CANRXD                                                                            | ,                     |              |      |      |      |

| High-Level Output Voltage  VCANTXD = VDDH, ICANRXD = -0.8 mA                                           | VOH                   | VDDH<br>-0.8 |      | VDDH | V    |

| Low-Level Output Voltage, V <sub>CANTXD</sub> = 0, I <sub>CANRXD</sub> = 1.6 mA                        | V <sub>OL</sub>       |              |      | 0.4  | V    |

| High-Level Output Current, V <sub>CANRXD</sub> = 0.7VDDH                                               | IOH                   |              |      | -800 | μА   |

| Low-Level Output Current, V <sub>CANRXD</sub> = 0.4V                                                   | loL                   |              |      | 1.6  | mA   |

| BUS Lines CANH, CANL                                                                                   | <u> </u>              |              |      | 1    |      |

| Output Voltage CANH (recessive) VCANTXD = VDDH; RL = open                                              | VCANH(r)              | 2.0          | 2.5  | 3.0  | V    |

| Output Voltage CANL (recessive) VCANTXD = VDDH; RL = open                                              | VCANL(r)              | 2.0          | 2.5  | 3.0  | V    |

| Output Current CANH (recessive)  VCANTXD = VDDH; VCANH, VCANL = 2.5V                                   | IO(CANH)(r)           |              |      | 100  | μА   |

| Output Current CANL (recessive)  VCANTXD = VDDH; VCANH, VCANL = 2.5V                                   | IO(CANL)(r)           | -100         |      |      | μА   |

| Output Voltage CANH (dominant), V <sub>CANTXD</sub> = 0V                                               | VCANH(d)              | 2.75         | 3.5  | 4.5  | V    |

| Output Voltage CANL (dominant), V <sub>CANTXD</sub> = 0V                                               | VCANL(d)              | 0.5          | 1.5  | 2.25 | V    |

| Differential Output Voltage (dominant) VCANH(d) - VCANL(d) VCANTXD = 0V                                | VOdiff(d)             | 1.5          | 2.0  | 3.0  | V    |

| Differential Output Voltage (recessive) VCANH(r) - VCANL(r) VCANTXD = VDDH                             | V <sub>Odiff(r)</sub> | 0            |      | 0.5  | V    |

| Differential Input Common Mode Voltage Range                                                           | Vсм                   | -2.0         |      | 7.0  | V    |

| Differential Receiver Threshold Voltage (recessive) VCANTXD = VDDH, VCANRXD < 0.4V, -2.0V < VCM < 7.0V | VRXDdiff(th)          | 0.5          | 0.75 | 1.0  | V    |

| Differential Receiver Input Voltage Hysteresis                                                         | Vldiff(hys)           | 0.10         | 0.2  | 0.30 | V    |

| Short Circuit Output Current CANH VCANH = -8.0V, VCANTXD = 0V                                          | ISC(CANH)             | -70          |      | -200 | mA   |

| Short Circuit Output Current CANL VCANL = VBAT = 18V, VCANTXD = 0V                                     | <sup>I</sup> SC(CANL) | 70           |      | 200  | mA   |

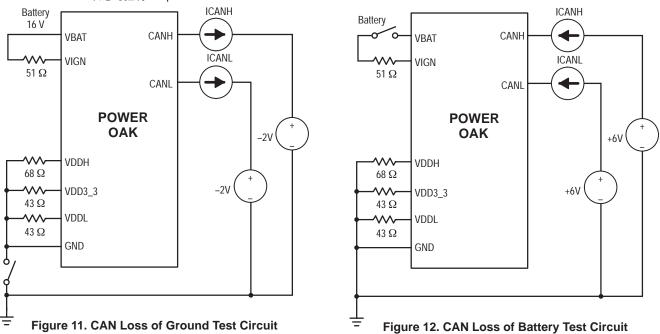

| Loss of Ground — see Figure 11. Refer to Figure 10 for loading con                                     | siderations.          |              | •    |      | -    |

| Output Leakage Current CANH, V <sub>CANH</sub> = -18V                                                  | IOLKG(CANH)           | -2.0         |      | 2.0  | mA   |

| Output Leakage Current CANHL, V <sub>CANL</sub> = -18V                                                 | IOLKG(CANL)           | -2.0         |      | 2.0  | mA   |

| Loss of Battery — see Figure 12. Refer to Figure 10 for loading con                                    | ` ,                   |              | •    | •    | •    |

| Input Leakage Current CANH, V <sub>CANH</sub> = 6.0V                                                   | ILKG(CANH)            | -800         |      | 800  | μА   |

| Input Leakage Current CANHL, V <sub>CANL</sub> = 6.0V                                                  | ILKG(CANL)            | -800         |      | 800  | μА   |

<sup>1.</sup> Guaranteed by design but not production tested.

| <u> </u>       |        |      |      |      |      |

|----------------|--------|------|------|------|------|

| Characteristic | Symbol | Min. | Тур. | Max. | Unit |

#### DC CHARACTERISTICS:

**CAN Transceiver (Continued)** (Bus Load CANH to CANL  $R_L = 60 \Omega$ ;  $Vdiff = V_{CANH} - V_{CANL}$ )

| CANH,CANL impedance                                                                             |                         |                         |     |      |     |    |

|-------------------------------------------------------------------------------------------------|-------------------------|-------------------------|-----|------|-----|----|

| CANH Common Mode Input Resistance                                                               |                         | Ri(CM)CANH              | 5.0 | 25   | 50  | kΩ |

| CANL Common Mode Input Resistance                                                               |                         | Ri(CM)CANL              | 5.0 | 25   | 50  | kΩ |

| CANH, CANL Common Mode Input Resistance Mismato 100(RiCANH - Ri(CM)CANL )/[ (RiCANH + Ri(CM)CAN | R <sub>i</sub> (CM)MCAN | -3.0                    |     | 3.0  | %   |    |

| Differential Input Resistance                                                                   |                         | R <sub>I(dif)</sub>     | 25  | 50   | 75  | kΩ |

| CANH Input Capacitance, V <sub>CANTXD</sub> = VDDH                                              | (Note 1)                | C <sub>I(CANH)</sub>    |     | 7.5  | 20  | pF |

| CANL Input Capacitance, VCANTXD = VDDH                                                          | (Note 1)                | C <sub>I(CANL)</sub>    |     | 7.5  | 20  | pF |

| Differential Input Capacitance, CINCANH - CINCANL, VCANTXD = VDDH                               | (Note 1)                | C <sub>I</sub> (CANdif) |     | 3.75 | 10  | pF |

| Thermal Shutdown                                                                                |                         |                         |     |      |     |    |

| Thermal Shutdown Junction Temperature                                                           | (Note 1)                | TS <sub>DIS</sub>       | 150 |      | 190 | °C |

| Thermal Shutdown Hysteresis                                                                     | (Note 1)                | TS <sub>HYS</sub>       | 5.0 |      | 20  | °C |

#### **AC CHARACTERISTICS:**

#### **CAN Transceiver**

| Timing Characteristics                                                                         |                    |  |  |     |    |  |  |  |

|------------------------------------------------------------------------------------------------|--------------------|--|--|-----|----|--|--|--|

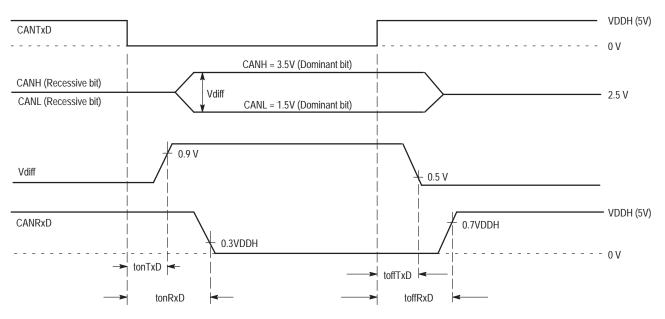

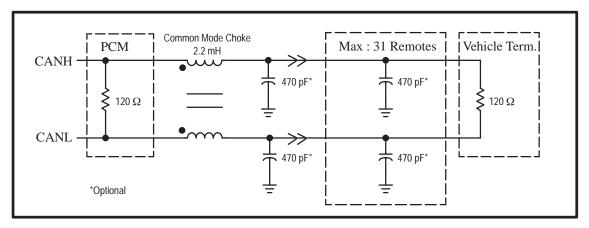

| See Figure 2, CANTXD = 250 kHz square wave; CANH & CANL Load $R_L$ = 60 $\Omega$ differential. |                    |  |  |     |    |  |  |  |

| Delay CANTXD to Bus Active, $C_L = 3nF$ $t_{OnTXD}$ 50 ns                                      |                    |  |  |     |    |  |  |  |

| Delay CANTXD to Bus Inactive, C <sub>L</sub> = 10pF                                            | toffTXD            |  |  | 80  | ns |  |  |  |

| Delay CANTXD to CANRXD, Bus Active, C <sub>L</sub> = 3nF                                       | t <sub>onRXD</sub> |  |  | 120 | ns |  |  |  |

| Delay CANTXD to CANRXD, Bus Inactive, C <sub>L</sub> = 10pF                                    | toffRXD            |  |  | 190 | ns |  |  |  |

#### NOTE:

1. Guaranteed by design but not production tested.

Figure 2. CAN Delay Timing Waveform

| Characteristic                                                                 | Symbol            | Min. | Тур. | Max. | Unit |

|--------------------------------------------------------------------------------|-------------------|------|------|------|------|

| DC CHARACTERISTICS:                                                            |                   |      |      |      |      |

| SPI                                                                            |                   |      |      |      |      |

| DO Output High Voltage, $I_{OH} = -100 \mu A$                                  | Voн               | 4.2  |      |      | V    |

| DO Output Low Voltage, IOL = 1.6 mA                                            | VOL               |      |      | 0.4  | V    |

| DO Tri-state Leakage Current, CS = 0                                           | IDOLkg            | -10  |      | 10   | μА   |

| CS, SCLK, DI Input High Voltage                                                | VIH               | 2.7  | 3.1  | 3.5  | V    |

| CS, SCLK, DI Input Low Voltage                                                 | V <sub>IL</sub>   | 1.7  | 2.1  | 2.5  | V    |

| CS, SCLK, DI Input Voltage Threshold Hysteresis                                | V <sub>Ihys</sub> | 0.8  | 1.0  | 1.2  | V    |

| CS, SCLK, DI Pull-Down Current,<br>CS, SCLK, DI = VDDH to V <sub>IL(min)</sub> | ISPI_PD           | 10   | 20   | 50   | μА   |

#### **AC CHARACTERISTICS:**

SPI

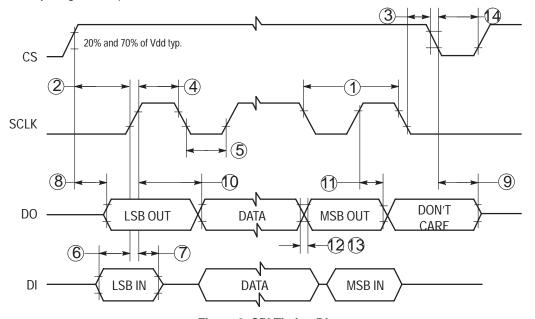

| 31 1   |                                             |           |                |                  |               |             |      |

|--------|---------------------------------------------|-----------|----------------|------------------|---------------|-------------|------|

| NOTES: | MPC565 QSMCM/ SPI set for CPHA = 0 & CPOL = | 0. *Assum | es MPC565 SCLK | rise and fall ti | mes of 30 ns, | DO load = 2 | 00pF |

| -      | Transfer Frequency                          |           | fop            | dc               |               | 5.00        | MHz  |

| 1      | SCLK Period                                 |           | tsck           | 200              |               | -           | ns   |

| 2      | Enable Lead Time                            |           | tlead          | 105              |               | -           | ns   |

| 3      | Enable Lag Time                             |           | tlag           | 50               |               | -           | ns   |

| 4      | SCLK High Time*                             |           | tsckhs         | 70               |               | -           | ns   |

| 5      | SCLK Low Time*                              |           | tsckls         | 70               |               | -           | ns   |

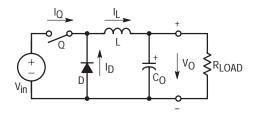

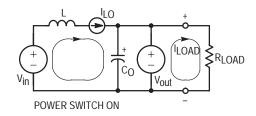

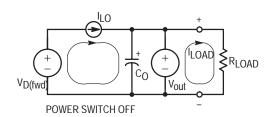

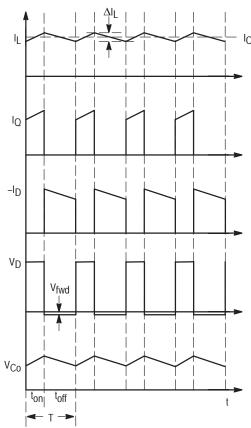

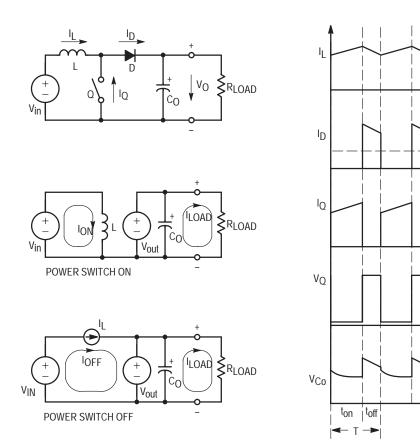

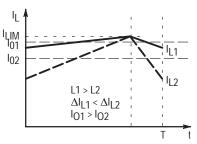

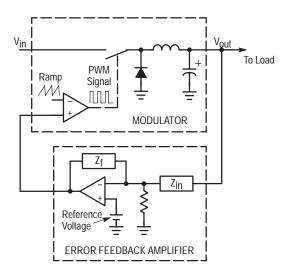

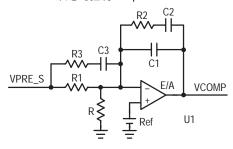

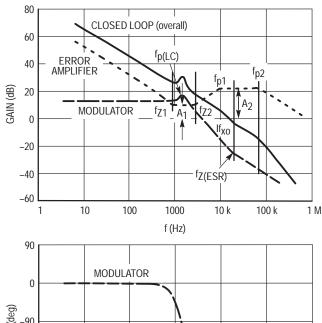

| 6      | SDI Input Setup Time                        |           | tsus           | 16               |               | -           | ns   |